## Application Note DC-010 DC/DC CONVERTERS

## **OUTPUT VOLTAGE ADJUSTMENT IN DC/DC CONVERTERS**

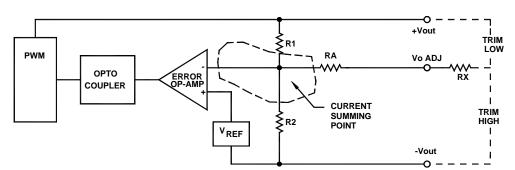

When the output voltage ( $V_0$ ) of a DC/DC converter must be adjusted in an application, the manufacturer usually specifies the output adjustable voltage range of the converter, typically 5% to 10%. The manufacturer provides an adjust terminal to be used by the customer for fine adjustment of  $V_0$ . For a better understanding of how it works, an error amplifier and reference voltage is shown in Figure 1.

The error OPAM compares the output voltage (V<sub>o</sub>) to a stable reference voltage and generates an error signal for the pulse width modulator (PWM). The PWM adjusts its duty cycle based on the error signal of the OPAM in order to keep V<sub>o</sub> constant under any line, load, and temperature variation.

It should be understood that a DC/DC converter is a linear system and utilizes negative feedback for control and stability. Also, the output accuracy of the converter depends only on the accuracy of the voltage reference, the open loop gain of the error amplifier, and the accuracy of the close loop component (such as R1, R2, RA, and RX in Figure 1). The opto-coupler and the PWM, together with the error OPAM, contribute to the dynamic or transient response of the converter (see References for more details). Referring to Figure 1, the output voltage with  $\rm V_{o}$  ADJ terminal open,  $\rm V_{o}$  is given by:

$$V_{o} = \left(\frac{R1}{R2} + 1\right) V_{REF}$$

Eq.1

When a lower V<sub>o</sub> is needed, the external RX resistor is placed between V<sub>o</sub> ADJ and +V<sub>o</sub>. The connection reduces the feedback resistor R1 and the new value of the feedback resistor is:

When a higher  $V_o$  is required RX is connected between the  $V_o$  ADJ terminal and  $-V_o$ . R2' is the parallel combination of R2 and the sum of RA+RX:

FIGURE 1. Typical output control stage of a DC/DC converter

Usually, RA is set for the maximum allowed  $\rm V_{\rm o}$  by the factory when RX=0.

Therefore: R2' =

$$\frac{R2(RA)}{R2+RA}$$

$\Rightarrow$  V<sub>o</sub> =  $\left(\frac{R1}{R2'} + 1\right)$ V<sub>REF</sub>

V<sub>o</sub> =  $\left(\frac{R1+R2'}{R2'}\right)$ V<sub>REF</sub>  $\frac{V_o}{V_{REF}} = \frac{R1+R2'}{R2'}$  R2' =  $\frac{R1}{\frac{V_o}{V_{REF}}} - 1$

$R2' = \frac{R1(V_{REF})}{V_{o} - V_{REF}}$

Eq.4

Substituting  $\frac{R2(RA)}{R2+RA}$  for R2´ in Eq.4 and solving for RA, we get:

$$RA = \frac{R1(R2)(V_{REF})}{R2(V_{o}-V_{REF})-R1(V_{REF})} \qquad Eq.5$$

NOTE:  $V_o$  in Eq.5 is not the nominal output of the converter, but the new higher  $V_o$ .

## EXAMPLE

Given R1 = 7.5k, R2 = 2.5k, V\_{\rm REF} = 2.5V, V $_{\rm O}$  Nominal = 10V:

For V<sub>o</sub> = 11V RA from Eq.5  $\cong$  18k $\Omega$

For lower  $V_0$ :

$$V_{o'} = \left(\frac{R1'}{R2} + 1\right) V_{REF}$$

Eq.6

$$\left(\frac{V_{o}}{VREF} - 1\right) = \frac{R1}{R2}$$

Let RA+RX = RT and  $\left(\frac{V_{o}'}{VREF} - 1\right) = K$ Then Eq.7 becomes R1' = KR2 and from Eq.2:

$$R1' = \frac{R1(RT)}{R1+RT}$$

Substituting Eq.8 into Eq.7 gives:  $\frac{R1(RT)}{R1+RT} = KR2$

$$RT = \frac{R1(R2)}{\frac{R1}{\kappa} - R2}$$

Eq.9

Using the same values given for the previous example: For V\_{\_O} = V\_{\_O}` = 9V, then RT  $\cong$  47k. Given RA = 20k, then RX = 27k.

From the example above, for a 10%  $V_o$  trim up (10V to 11V) RA+RX=18k and for 10%  $V_o$  trim down (10V to 9V) RA+RX=47k. It is obvious that for a given RA, the trim down range of the converter is much higher than that of the trim up. In order not to exceed the manufacturer's recommended trim down range, a series resistor with RA is required and its value can be calculated from Eq.6 through Eq.9.

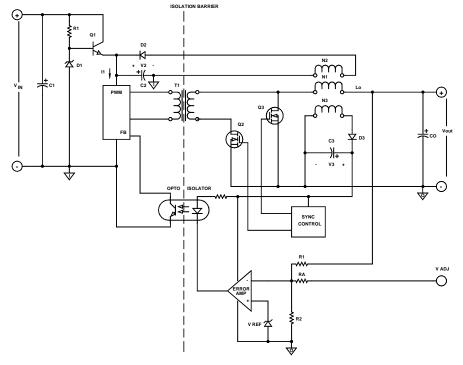

By adjusting V<sub>o</sub>, the bias voltages of V2, V3 increase or decrease. The value of V2 is calculated to be V2≥VD1 in order to turn and keep off Q1 under normal operating conditions. When V2 becomes lower than VD1 through the output voltage adjustment, Q1 is ON continuously and the power dissipated in it is Pd<sub>q1</sub>=(V1-VD1)I1, which can cause failure of Q1. If V2 is trimmed higher than the reverse break-

FIGURE 2. Typical bias circuits in a DC/DC converter

You may be wondering why the  $\pm 10\%$  V<sub>o</sub> ADJ range cannot be exceeded. The answer is simple: it was designed for  $\pm 10\%$  maximum for the following reason:

The circuit in Figure 2 shows the auxiliary bias supplies used in an isolated DC/DC converter. The internal bias voltage for the input L0, D2, C2 and the output L0, D3, C3 are generated through magnetic coupling of the output inductor L0 in Figure 2. The value of V2 and V3 with  $V_o$  ADJ open are given by the following equations:

$$V2 = \frac{N2}{N1} V_{o}$$

Eq.10

$$O'$$

$$V2 = \frac{N2}{N1} \left(\frac{R1}{R2} + 1\right) V_{REF}$$

$$V3 = \frac{N3}{N1} V_{o}$$

Eq.11

$$Or$$

$$V3 = \frac{N3}{N1} \left(\frac{R1}{R2} + 1\right) V_{REF}$$

down voltage of the  $V_{BE}$  junction of Q1, which is 3V to 6V higher than the base voltage of VD1, Q1 will fail.

The output bias voltage V2, which biases the error amplifier and control circuit, is designed for optimum value for switching the synchronous rectifier transistor Q2, Q3. When  $V_o$  is adjusted below the specified value, the output of the error OPAM may saturate, which in turn, affects  $V_o$  line and load regulation.

A lower V3 can also affect the efficiency of the converter if Q2, Q3 are forced to operate longer in their linear region (Ohmic region). When the output voltage trim exceeds the maximum range, it may destroy the output overvoltage protection zener diode D4 and also lower the efficiency by overdriving the gate to source  $C_{GS}$  of Q2 and Q3.

When a potentiometer is used for fine adjustment of the output, make sure for the initial turn on that the arm is set to the middle. In high output voltage converters, one **must** take into consideration the power rating of the selected resistor or potentiometer.

## REFERENCES

Pressman, Abraham I. Switching Power Supply Design. Mcgraw-Hill, Inc.1991.