# beta dyne

## Key Features

- Efficiency 87%

- Six-sided shielding

- Power density of 98W/in<sup>3</sup>

- 100µS transient response time

- 500µA off state current

- Output synchronous rectification

- Input-to-output isolation

- Soft start

- Short circuit protection

- Thermal protection

- Undervoltage protection

- External synchronization

Beta Dyne is protected under various patents, including but not limited to U.S. Patent numbers: 5,777,519; 6,188,276; 6,262,901; 6,452,818; 6,473,3171.

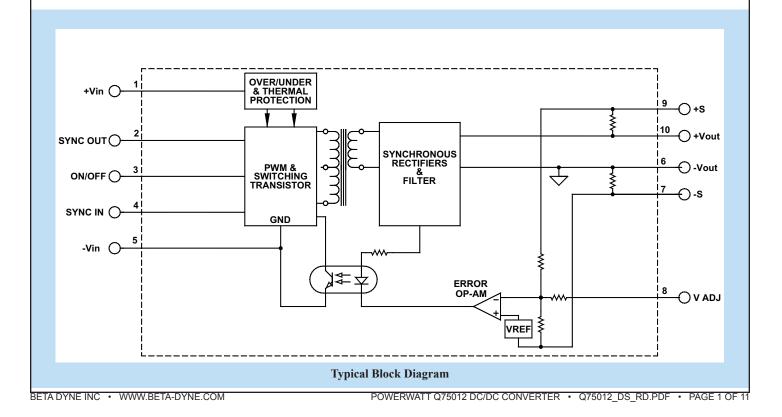

# **Functional Description**

The Q75012 is a DC/DC Converter that accepts  $23-25V_{IN}$  & provides  $4V_{OUT}$ @18A. The converter is designed to synchronize to external clock of 400kHz.

| NOTICE: Do not operate this converter with a float-           |  |

|---------------------------------------------------------------|--|

| ing case. Connect the case to either $+V_{IN}$ or $-V_{IN}$ . |  |

# Electrical Specifications

Unless otherwise specified, all parameters are given under typical ambient temperature of  $+25^{\circ}$ C with an airflow rate = 400LFM. With the given power derating, the operating range is  $-40^{\circ}$ C to  $+125^{\circ}$ C. Specifications subject to change without notice.

| PARAMETER                        | CONDITION / NOTE                            | MIN | ТҮР  | MAX | UNIT                  |

|----------------------------------|---------------------------------------------|-----|------|-----|-----------------------|

| Input Voltage Range              |                                             | 23  | 24   | 25  | V                     |

| Input Filter                     | Capacitor                                   |     |      |     |                       |

| Reflected Ripple                 |                                             |     | 150  |     | mA <sub>PP</sub>      |

| No Load Input Current            |                                             |     | 160  |     | mA                    |

| Full load Input Current          |                                             |     | 3398 |     | mA                    |

| Input Surge Current (20µS Spike) |                                             |     |      | 10  | A                     |

| Short Circuit Current Limit      |                                             |     | 125  | 150 | % I <sub>IN</sub> Max |

| Off State Current                |                                             |     | 150  |     | μA                    |

| Remote ON/OFF Control            |                                             |     |      |     |                       |

| Supply ON                        | Pin 5 Open (Open circuit voltage: 12V Max.) |     |      |     |                       |

| Supply OFF                       |                                             | 0   |      | 0.8 | Vdc                   |

| Logic Input Reference            | -Vin                                        |     |      |     |                       |

| Logic Compatibility              | TTL Open Collector or CMOS Open Drain       |     |      |     |                       |

| Sync In Pulse Width              |                                             | 300 |      |     | nS                    |

| Sync Out Source Current          |                                             | 2.5 | 5    |     | mA                    |

#### **OUTPUT SPECIFICATIONS**

| PARAMETER                     | CONDITION / NOTE                                   | MIN | ТҮР   | MAX  | UNIT            |

|-------------------------------|----------------------------------------------------|-----|-------|------|-----------------|

| Voltage                       |                                                    |     | 4     |      | V <sub>DC</sub> |

| Output Voltage Accuracy       |                                                    |     | ±1    | ±2   | %               |

| Output Voltage Adjustment     |                                                    |     | ±5    | ĺ    | %               |

| Output Current                |                                                    |     | 18    | ĺ    | A               |

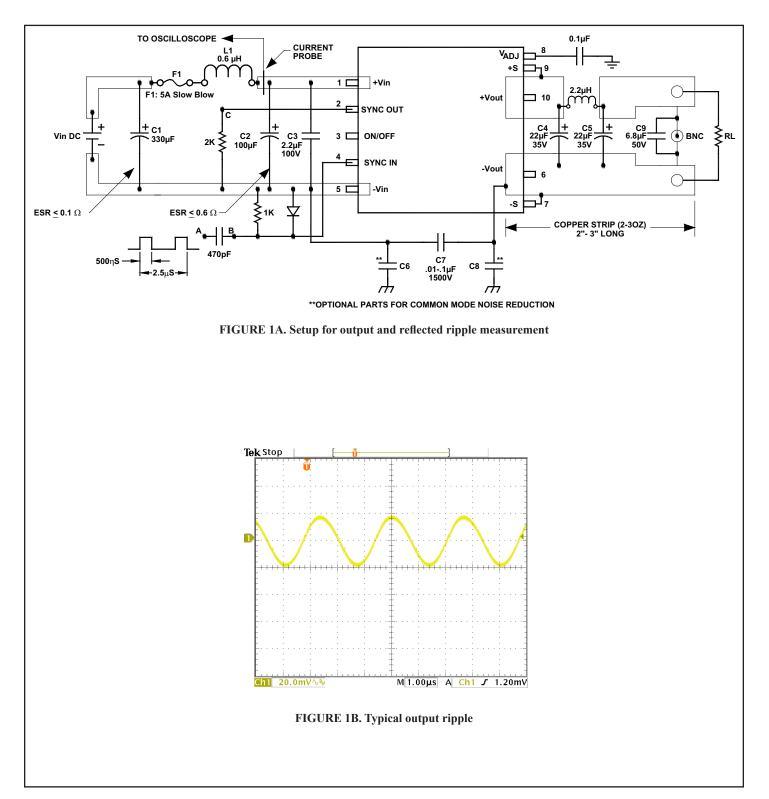

| Ripple & Noise                | See Figure 1B                                      |     | 36    | ĺ    | mV              |

| Line Regulation               | Minimum V <sub>IN</sub> to maximum V <sub>IN</sub> |     | ±0.25 | ±0.5 | %               |

| Load Regulation               | 10% FL to FL                                       |     | ±0.25 | ±0.5 | %               |

| Output Minimum Load           |                                                    | 5   | 10    | ĺ    | %               |

| Temperature Coefficient @ FL  |                                                    |     | 0.02  | ĺ    | %/°C            |

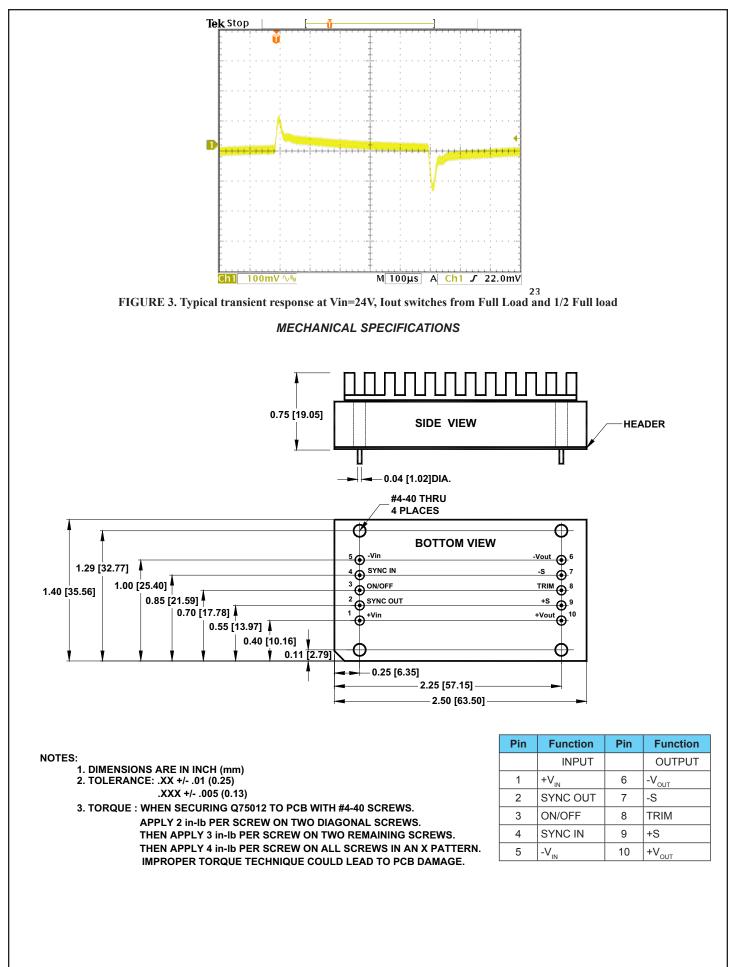

| Transient Response Time       | 50% FL to FL to 50% FL, See Figure 3               |     | 50    | 100  | μS              |

| Short Circuit Protection      | By input current limiting                          |     |       | ĺ    |                 |

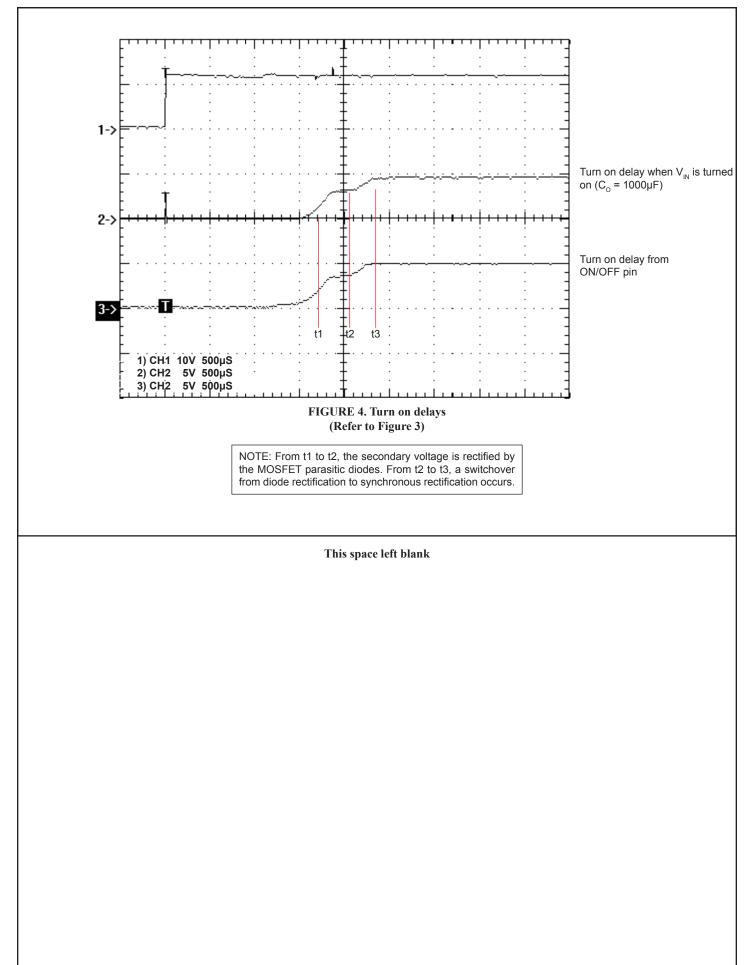

| Turn On Delay with Soft Start | See Figure 4                                       |     | 3     | 4    | mS              |

| Output Overvoltage Protection | None                                               |     |       |      |                 |

#### **GENERAL SPECIFICATIONS**

| PARAMETER                                   | CONDITION / NOTE | MIN | ТҮР             | MAX | UNIT |

|---------------------------------------------|------------------|-----|-----------------|-----|------|

| Efficiency (at full power)                  |                  |     | 87              |     |      |

| Isolation Voltage (1 min.), Input to Output |                  |     | 1500            |     | Vdc  |

| Isolation Resistance                        |                  |     | 10 <sup>9</sup> |     | Ω    |

| Isolation Capacitance                       |                  |     | 300             |     | pF   |

| Switching Frequency                         |                  | 360 | 380             | 390 | kHz  |

| Synchronization Frequency                   |                  |     | 400             |     | kHz  |

#### **ENVIRONMENTAL SPECIFICATIONS**

| PARAMETER                                       | CONDITION / NOTE                                            | MIN | ТҮР                 | MAX  | UNIT  |

|-------------------------------------------------|-------------------------------------------------------------|-----|---------------------|------|-------|

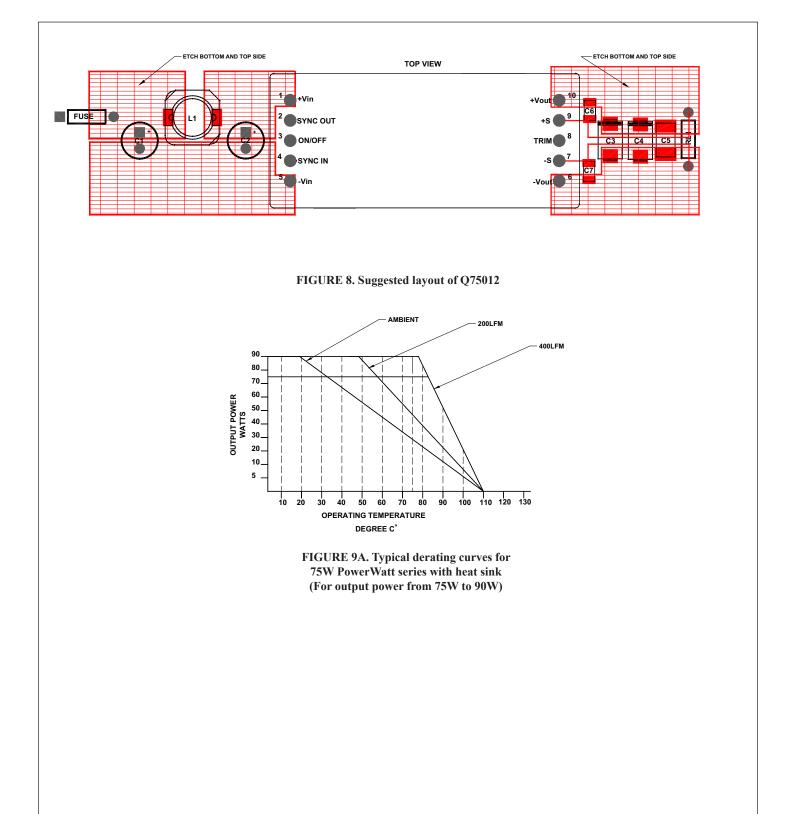

| Operating Temperature Range (Ambient)           | Industrial, See Figure 9A & 9B                              | 25  |                     | 60   | °C    |

| Storage Temperature Range                       |                                                             | -55 |                     | +150 | °C    |

| Maximum Operating Case Temperature              |                                                             |     |                     | 110  | °C    |

| Thermal Resistance, With Heat Sink <sup>3</sup> | Zero air flow                                               |     | 7.8                 |      | °C/W  |

| Case Connection                                 | CASE MUST BE CONNECTED TO EITHER INPUT OR OUTPUT POWER PINS |     |                     |      |       |

| MTBF                                            | Per MIL-HNBK-217F (Ground benign, +25°C)                    |     | 1.1×10 <sup>6</sup> |      | hours |

#### PHYSICAL CHARACTERISTICS

| PARAMETER                          | CONDITION / NOTE                          | MIN | ТҮР | MAX | UNIT |

|------------------------------------|-------------------------------------------|-----|-----|-----|------|

| Dimensions, With Heat Sink (L×W×H) | 2.50×1.40×0.750 in. (63.50×35.56x19.05mm) |     |     |     |      |

| Weight, With Heat Sink             | 3.2 oz. (90g)                             |     |     |     |      |

<sup>1</sup> The maximum input current at any given input range measured at minimum input voltage is given as 1.6\*I<sub>NOMINAL</sub>. Nominal input current is the typical value measured at the input of the converter under full-load room temperature and nominal input voltage (24Vdc).

<sup>2</sup> Measured with 22μF capacitor for 100μF capacitor for 24V<sub>IN</sub> at the input power pins in series with 10μH inductor (see Figure 1A). <sup>3</sup> See Application Note DC-004: Thermal Considerations for DC/DC Converters.

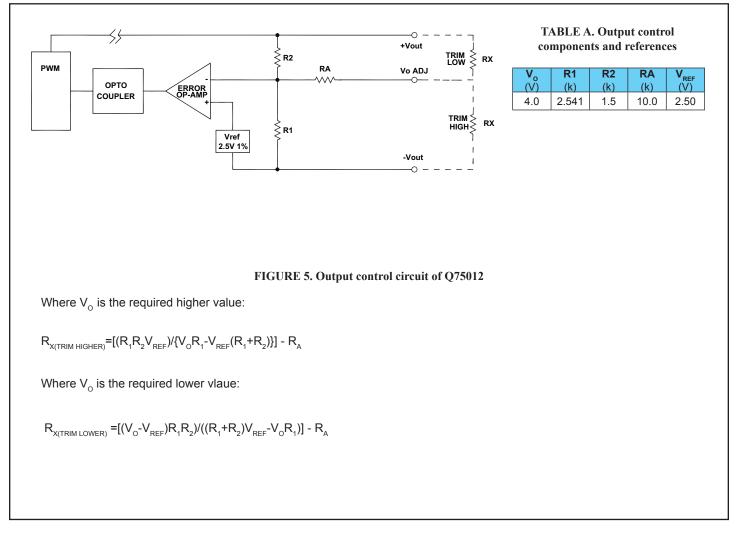

#### EXTERNAL TRIMMING OF OUTPUT VOLTAGES

To trim the output voltage DOWN, connect a 5% ¼W resistor between the + (plus) output and trim pin of the converter. To trim the output voltage UP, connect a 5% ¼W resistor between the – (minus) output and trim pins of the converter. For UP/DOWN trimming capability, connect a 10k $\Omega$  potentiometer between the + and – output pins, with the wiper arm connected to the trim pin.

The trim resistors/potentiometer can be connected at the converter output pins or the load. However, if connected at the load,

the resistance of the runs becomes part of the feedback network which improves load regulation. If the load is some distance from the converter, the use of #20 gauge wire is recommended to avoid excessive voltage drop due to the resistance of the circuit paths.

#### See our application notes:

DC-001: Testing Transient Response in DC/DC Converters DC-004: Thermal Consideration for DC/DC Converters

#### **EXTERNAL SYNCHRONIZATION**

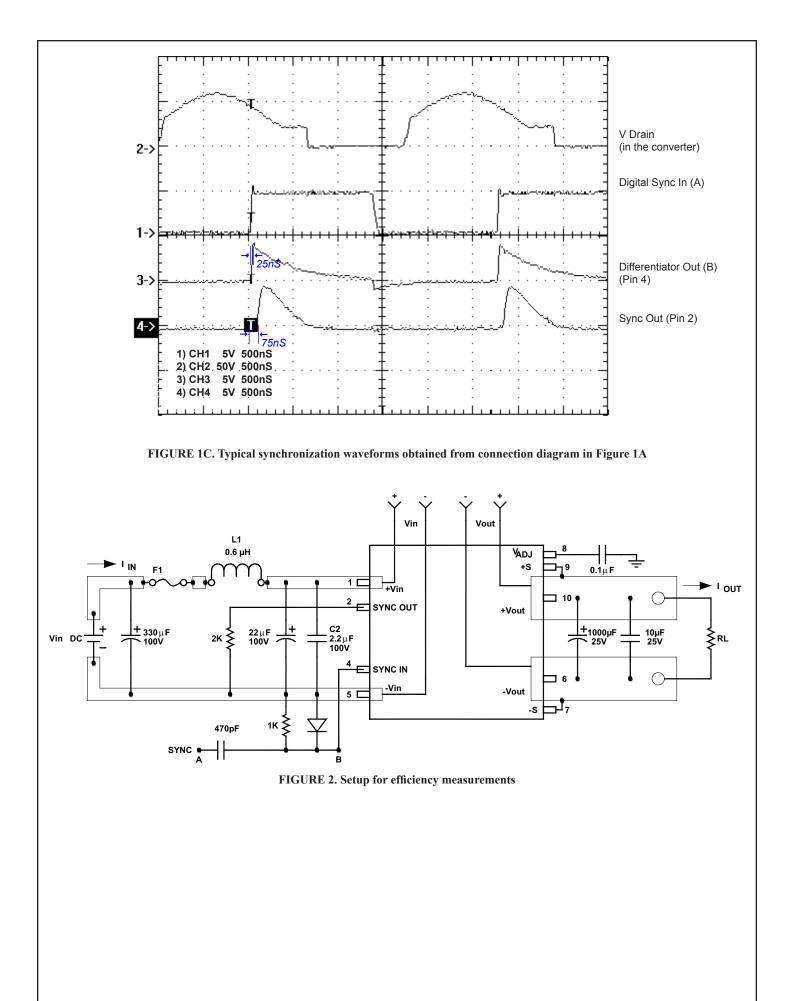

A TTL signal applied at the SYNC pin of the converter will synchronize the switching frequency of the converter to that of the TTL input signal. The external (TTL) frequency must be equal or higher than the converter's frequency. At the positive-going edge of the applied pulse, the internal power-switching transistor turns off and the PWM discharges its timing capacitor. At the negative-going edge, the PWM resumes normal operation. The minimum positive pulse width of the TTL signal must be 300nS and its frequency between 400kHz and 410kHz.

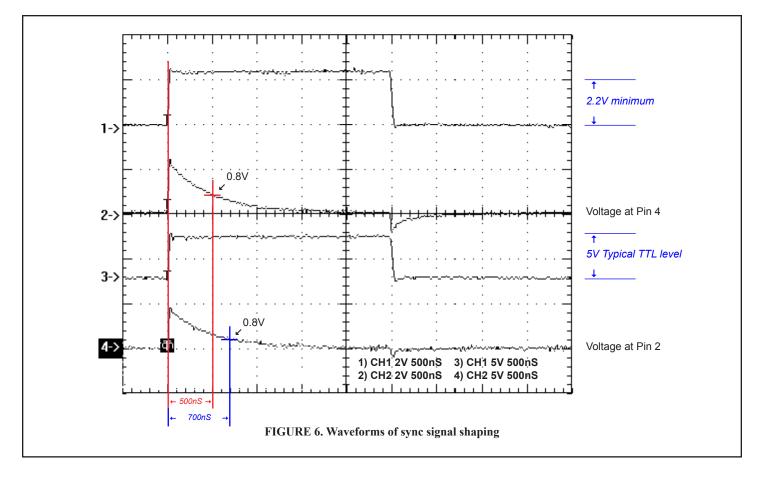

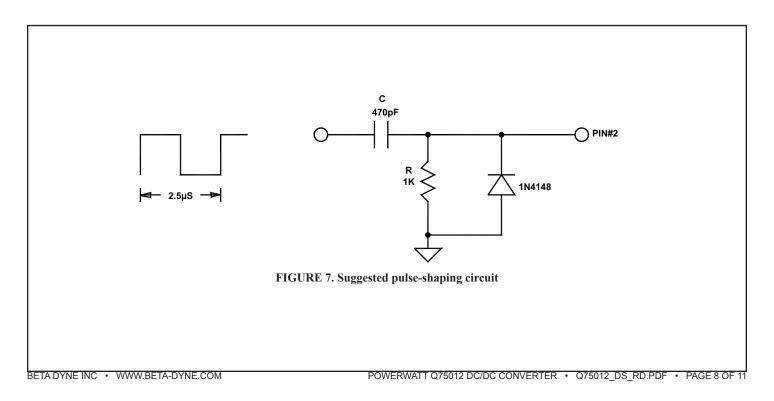

NOTE: Higher frequencies will reduce the efficiency of the converter and wide TTL pulses will force the PWM to follow the external TTL width modulation, which may affect regulation. A high TTL signal at the SYNC pin of the converter will turn the converter off. An internal pull-down resistor will keep this pin low when it is not used. A pulse differentiator (see Figure 7) can be used to shape a square wave sync signal as shown in Figure 6.

To avoid noise pickup, install a  $1k\Omega$  resistor from the SYNC IN (Pin 4) to  $-V_{_{\rm IN}}$  (Pin 5). An internal current source will provide BETA DYNE INC • WWW.BETA-DYNE.COM PO

2.5mA of current for driving another 75W converter from the SYNC OUT (Pin 2).

Please note that when the SYNC OUT pin is used to drive multiple converters, the  $1k\Omega$  sync input resistor is not required. However, a  $2k\Omega$  resistor load must be installed at the SYNC OUT pin (Pin 2) of the driving converter. The  $2k\Omega$  resistor can be the parallel combination of individual sync in resistors installed at the SYNC IN pin (Pin 4) of the converters to be driven.

For example, if a 75W converter "master" will be used to synchronize five other 75W converter "slaves," a  $10k\Omega$  resistor can be installed at the SYNC IN pin of each slave, and the SYNC OUT pin of the master can be connected to all the SYNC IN pins of the slaves.

The parallel combination of five  $10k\Omega$  resistors will provide the  $2k\Omega$  sync out load for the master. Avoid overloading the sync output current source with a resistor lower than  $2k\Omega$ . Overloading may affect the performance of the converter.

#### SYNC SIGNAL SHAPING

As described in External Synchronization, the PWM of the converter requires a TTL signal of 0.8 to 2Vdc minimum amplitude and minimum duration of 300nS. When such a signal is not available (through one shot multivibrator or other pulse-shaping circuits) a C-R differentiator, such as the one in Figure 7, can be used to shape a square wave TTL signal. As is shown by the oscillogram in Figure 6, the positive edge of the sync pulse must be 2V minimum and the

decaying exponential must reach the low er threshold of 0.8Vdc in 300nS minimum from the positive edge. The parallel diode with the resistor is a small signal switching diode or a Schottky signal diode with 0.3 to 0.5V forward drop, it is used to clamp the voltage at Pin 2@-0.5Vdc. For other logic levels (such as 2.5 and 3.3), adjust the RC time constant to obtain the required timing.

#### APPLICATION CONSIDERATIONS

**Pin Functions**

+V<sub>IN</sub> (Pin 1): For positive input power supply connections.

SYNC OUT (Pin 2): Output-driving signal of the PWM.

**ON/OFF** (Pin 3): Turns converter off when pulled to ground through an open collector or open drain transistor. Maximum voltage at this pin is 12V minus a diode drop. Can be parallel connected with the ON/OFF pins of multiple converters or any Beta Dyne converter that may reside in the system. Leave this pin open for continuous operation.

**SYNC IN** (Pin 4): Input synchronization signal to the PWM. Used to synchronize the converter to an external frequency source.

$\textbf{-V}_{\text{IN}}$  (Pin 5): For negative input power supply connection (or input ground).

-V<sub>out</sub> (Pin 6): Negative output (GND).

-S (Pin 7): Negative output voltage sense; to be connected to the negative output at the load only.

$V_{ADJ}$  (Pin 8): Output voltage adjust; to be used for an output voltage adjustment. Bypass this pin with a 0.01µF to 0.10µF capacitor.

**+S** (Pin 9): Positive output voltage sense; to be connected to the positive output voltage at the load only.

The impedance of an output filter may also affect the stability

of a converter when additional low-pass filters are used. If additional

output ripple reduction is required, avoid installing series inductors at

the output. Instead, try to maximize output capacitance. The inductor

of the output copper strips and a 1000µF capacitor will be enough

for most applications. Low ESR electrolytic or tantalum capacitors

can be used for additional output ripple reduction in parallel with ceramic capacitors for high-frequency attenuation. We recommend

Vishay Sprague 594D Solid Tantalum Chip Capacitors.

### DESIGN CONSIDERATIONS

#### Input Source Impedance

The input of the converter should be connected to a low AC-impedance source. To reduce the impedance of a potentially high-inductive DC source, use a low ESR electrolytic capacitor (ESR < 0.6W@400kHz) mounted as close to the input pins as possible to ensure stability of the converter. As suggested in Figures 1 through 3, an electrolytic capacitor (22µF for 48V<sub>IN</sub> or 47µF to 100µF for 24V<sub>IN</sub>) in parallel with an SMD 2.2µF ceramic capacitor will ensure stability under any line or load condition. The 330µF capacitor before the input inductor L1 will reduce both reflected ripple and any long wire impedance from the DC source.

#### THERMAL CONSIDERATIONS

The heat generated by the converter is transferred to the ambient by air conduction. At room temperature without any air movement, the operating environment of the converter is higher than room temperature,  $25^{\circ}$ – $50^{\circ}$ C higher, due to the fact that air around the converter heats up.

To measure the actual operating environment of the converter in a still air environment, place a thermocoupler a half-inch above the top center of the converter. Perform the same temperature measurement in a forced air convection system and use those temperature values for your thermal calculations. Do not assume the temperature is constant throughout a forced air cooling system! Surrounding components and the load can cause the converter to go to thermal shutdown.

**Output Filter Impedance**

The minimum junction temperature of all semiconductors is 150°C and the maximum operating temperature of the PCB is 150°C. When the temperature of the PCB reaches approximately 125°C, the converter will turn off. The thermal hysterisis of 20°–30°C will allow the converter to cool off and resume operation once it reaches approximately 95°C. If there is not enough air circulation due to air fan failure of the system or very high environmental temperatures, the converter will stay in this so-called "hiccup" (ON/OFF) thermal mode indefinitely.

#### **EFFICIENCY MEASUREMENTS**

Using the setup given in Figure 2, measure the input and output voltage at the pins at the top of the multiplayer PCB and use these values to calculate the efficiency. The voltage drop at full load at the output (20A when measured from the top of the PCB to the other end of the pin) is 18mV at room temperature. Even though 18mV

does not look bad, it accounts for approximately 0.4W of power dissipation for both the positive and negative output pins for a total power dissipation of 0.8W. A poor layout can cause this worst-case scenario; see *Layout Considerations* for more details.

#### SHORT CIRCUIT PROTECTION

The converter has a dual short circuit protection feature. At the input side of the converter, two short circuit current comparators are used to monitor the input current of the converter. They are biased at different voltage levels; the lower threshold (LTH) comparator provides the power limiting function of the converter. Under normal operating conditions, the LTH comparator limits the output power of the converter when the maximum output power is exceeded. When a hard short is applied across the output of the converter and the input current exceeds the set threshold of the second comparator,

the converter goes into shutdown mode, the overcurrent latch is set and the converter is turned off. The converter will turn on again when its input voltage is recycled (OFF–ON) or if the ON/OFF pin is used to turn the converter on and off. The time required for the ON/OFF pin to be held low is between 100mS and 800mS.

#### LAYOUT CONSIDERATIONS

The maximum output current of this converter is 18A and is carried to the load through six 10A rated pins. When the converter is installed in a double-sided PCB, use both sides to connect the high current pins and use 2–3oz. copper for the plated through holes and/or power pads.

Please note that in a multilayer PCB the inner layers do not contribute much in reducing the thermal resistance of the power component, they only reduce the resistance to the load. If the top and bottom layers of your PCB can be plated up to 3–4 oz., you do not have to use a multilayer PCB for the converter.

If the sense run length exceeds 2 inches, the sense pins may have to be bypassed at a point close to the converter. Keep in mind to bypass sense pins to their respective polarity, and avoid running digital signal lines parallel to the sense pins. If more than one power device or converter is used per system board, use a star ground connection for all power devices.

#### EMI/RFI IN DC/DC CONVERTERS

All switching AC/DC and DC/DC converters generate noise due to high-voltage, high-current internal switching. Conducted noise is the noise that appears at the point of conduct (pins) of the converter. Radiated noise is the electromagnetic noise transmitted to the environment from the power source. Conducted noise can be reduced to acceptable levels by an input/output low-pass filter.

Manufacturers commonly use metal cases and conductive headers to provide six-sided shielding and to prevent radiated noise. The Q75012 provides six sided shielding by connecting the aluminum heat sink to the header. The whole case assembly can be connected to either +V<sub>IN</sub> (for 48V<sub>IN</sub>) or -V<sub>IN</sub> (for 24V<sub>IN</sub>) through the four threaded holes on the bottom of the converter. NOTE: The bottom of the converter is insulated with the non-conductive side of the header.

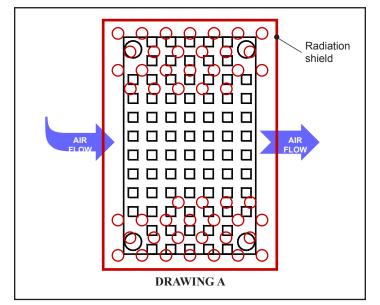

Effective placement and orientation of the converter in a system with forced air cooling can reduce the case temperature by 5–15°C (depending on the air flow (LFM)). When the converter is

placed at the entrance and air passes over it as shown in Drawing A—from Pin 5–1 and 6–10—the lowest case temperature can be obtained.

Therefore, converters require special consideration in three critical areas—layout, radiation and cooling—that may create conflicts. We stress the importance of these critical areas:

When an open-frame converter is used to power digital circuits, radiation shielding can be implemented via the system shielding. When the load is an analog circuit—for example, A/D, D/A, RF amplifier, etc.—and these components are placed close to the converter, the radiated noise may affect signal integrity.

High impedance summing points of operational amplifiers or other components with poor power supply rejection ratio (PSRR) may be affected. In this case, local radiation shielding around the converter is necessary.

When noise creates problems in a system, it is very difficult to identify the source of the problem. A poor layout with ground loop can not only create noise it can also affect the stability of the converter or randomly trigger an event. A common problem in high frequency and high power density DC/DC converters is the so-called "common-mode noise," which is the noise generated from parasitic capacitors, leakage inductance, etc. in the converter.

Common-mode noise (CMN) can be bypassed to chassis with small capacitors between input and output grounds to chassis and input and output ground. Assuming the layout is correct and the converter still generates noise, the question then becomes why does the system not exhibit a noise problem when a linear voltage source is supplied?

The answer comes from the process of elimination. Replacing a switching power source of 500kHz with another one switching at 50–60Hz is not the solution. Using the "noisy" DC/DC converter, one may try the following: First, if possible, shield the converter with six-sided shielding. If the problem is still in the system, then radiated noise is not the problem! Conducted noise or poor layout are the more likely causes. As was mentioned earlier, the use of a component with poor PSRR—e.g. BICMOS, CMOS, rail-to-rail OPAMS—may be the cause of the problem.

Do not use a converter with 50mV to 100mV output ripple to power a 12-bit A/D converter. Also keep in mind that CMOS, OPAMs, A/D, and S/H may offer low power, but the parasitic capacitor from drain to gate, drain to source, and gate to source will couple any V<sub>DD</sub> and V<sub>SS</sub> supply noise into your signal.

Better filtering in the input or output will reduce conducted noise if they are the cause of the problem. When both radiated and conducted noise are reduced, the last potential cause is *layout*. Also, use ground plain under the converter for shielding and avoid passing signal lines under it.

In conclusion, open-frame DC/DC converters offer high efficiency, power density and low cost, but radiate a wide band of noise. For any application where the system layout is critical, select the appropriate converter(s) for the application and completely test your system during the prototyping phase. DO NOT ASSUME all is well. To make sure your prototype is functioning properly, perform a complete evaluation.

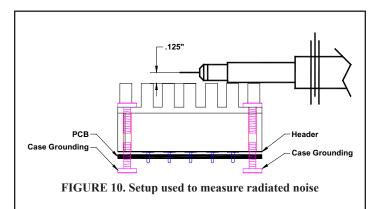

#### EMI/RFI PERFORMANCE OF THE Q75012

The Q75012 with its aluminum case and heat sink offers not only an extended operating range, but reduced radiated noise by forming an electromagnetic shield around itself when the heat sink is grounded. To test the effectiveness of the shield, the following (admittedly crude) setup was used (see Figure 10). A voltage probe was placed 0.125 inches above the center of the heat sink. With the converter under full load, two sets of data were taken at each of the following bandwidths: 6.2MHz and 50MHz. One of the data sets was taken with a floating heat sink, the other with a grounded heat sink at the input ground. The grounded heatsink was found to reduce the radiated noise.